1 段页式内存管理机制

在x86 CPU中,采用了段页式内存管理机制,分段和分页模型。

-

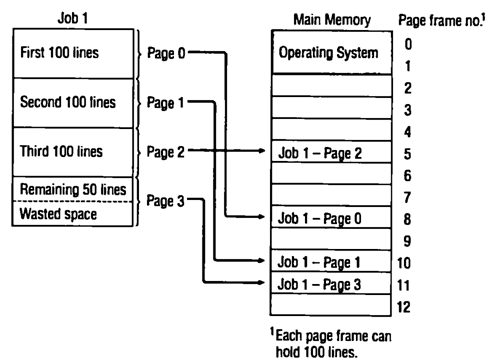

分页(Paging)机制

逻辑地址由页号和偏移量组成。

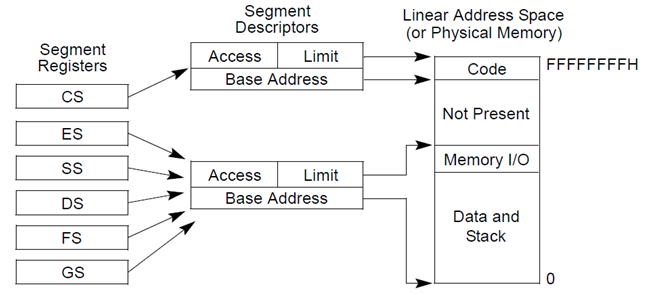

- 分段(Segment)机制

分段允许程序员把存储器看成由多个地址空间或段组成。程序和相关的数据被划分成一组段(segment),不要求所有程序的所有段都有相同长度。

和分页一样,分段情况下的逻辑地址由两部分组成:段号和偏移量。

分段的优点:

- 简化不断增长的数据结构处理。

- 允许程序独立地改变或重新编译,而不要求整个程序集合重新链接和重新加载。

- 有助于进程间的共享。

- 有助于保护。由于一个段可以被构造成包含一个明确定义的程序或数据集,程序员或系统管理员可以以一种方便的形式指定访问权限。

- 虚拟内存

内存的基本思想是程序、数据、堆栈的总大小可以超过可用物理内存的大小,操作系统把程序当前使用的那些部分保留在内存中,而其他部分保存在磁盘上。

虚拟内存的实现基于分页技术。

虚拟内存的优点:

- 在内存中可以同时运行多个进程

- 进程可以比内存全部空间还大,不再局限于物理内存大小

-

内存更高效地被使用

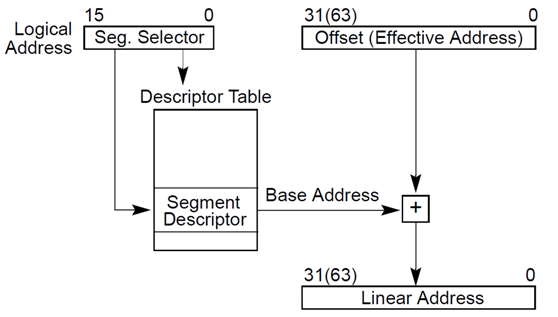

2 逻辑地址到线性地址的映射过程

X86 CPU逻辑地址到线性地址映射过程如下图:

逻辑地址到线性地址映射过程如下:

(1)根据指令的性质来确定应该使用哪一个段寄存器(Segment Selector),例如转移指令中的地址在代码段,而取数据指令中的地址在数据段;

(2)根据段存器的内容,找到相应的“地址段描述结构“(Segment Descriptor),段描述结构都放在一个表(Descriptor Table)中(GDT或LDT、TR、IDT),而表的起始地址保存在GDTR、LDTR、IDTR、TR寄存器中。这就是4个内存管理寄存器GDTR、LDTR、IDTR和TR的用途;

(3)从地址段描述结构中找到基地址(Base Address);

(4)将指令发出的地址作为位移(Effective Address),与段描述结构中规定的段长度相比,看看是否越界;

(5)根据指令的性质和段描述符中的访问权限来确定是否越权;

(6)将指令中发出的地址作为位移,与基地址相加而得出线性地址(Linear Address)。

问题: 1、逻辑地址就是CPU指令发出的地址,那么段选择码(Segment Selector)的值在哪里? 2、知道段选择码后,需要从描述符表(Descriptor Table)中找到相应的表项,那怎么知道描述符表在内存中哪个位置?

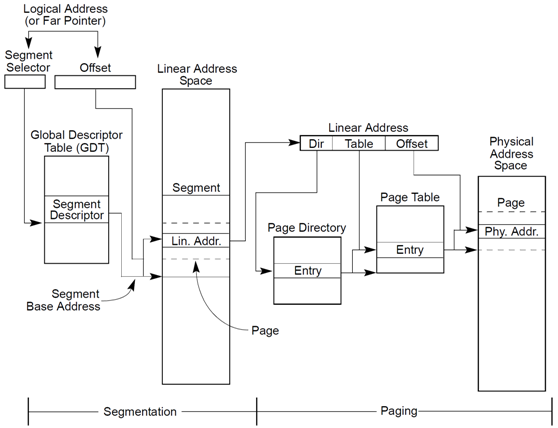

3 线性地址到物理地址的映射过程

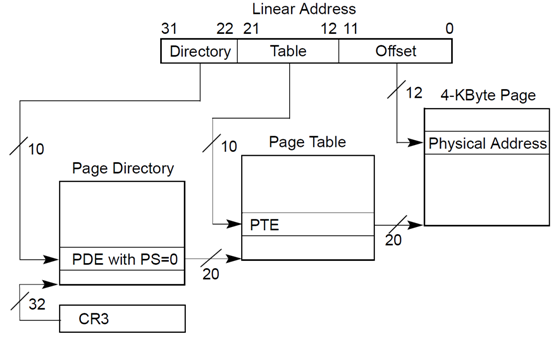

X86 CPU线性地址到物理地址映射过程:

线性地址到物理地址映射过程如下:

(1)从CR3寄存器中获取页面目录表(Page Directory)的基地址;

(2)以线性地址的Directory位段为下标,在目录(Page Directory)中取得相应页面表(Page Table)的基地址;

(3)以线性地址中的Table位段为下标,在所得到的页面表中获得相应的页面描述项;

(4)将页面描述项中给出的页面基地址与线性地址中的offset位段相加得到物理地址。

问题: CR3寄存器的值从哪里来的?

CR3 寄存器里面的值是 task_struct 里面pgd 的值吧, 每一次切换进程的时候都会把pgd 更新到CR3 寄存器. 是这样么?

是的。

有个问题请教,为什么会存在两个虚拟地址映射到同一个物理地址?